在集成电路制造、测试和应用过程中,电气过应力(Electrical Overstress,EOS)是导致芯片失效的最常见原因之一。据行业统计,EOS相关损伤占半导体器件场内返修的20%~40%。不同于瞬态的ESD(静电放电),EOS通常持续时间更长、能量更高,可源于电源异常、浪涌、误操作或系统级过载。芯片级EOS测试通过模拟这些过应力场景,评估内部结构耐受能力,帮助设计师优化防护、提升产品鲁棒性,在先进制程和车规级芯片领域尤为关键。

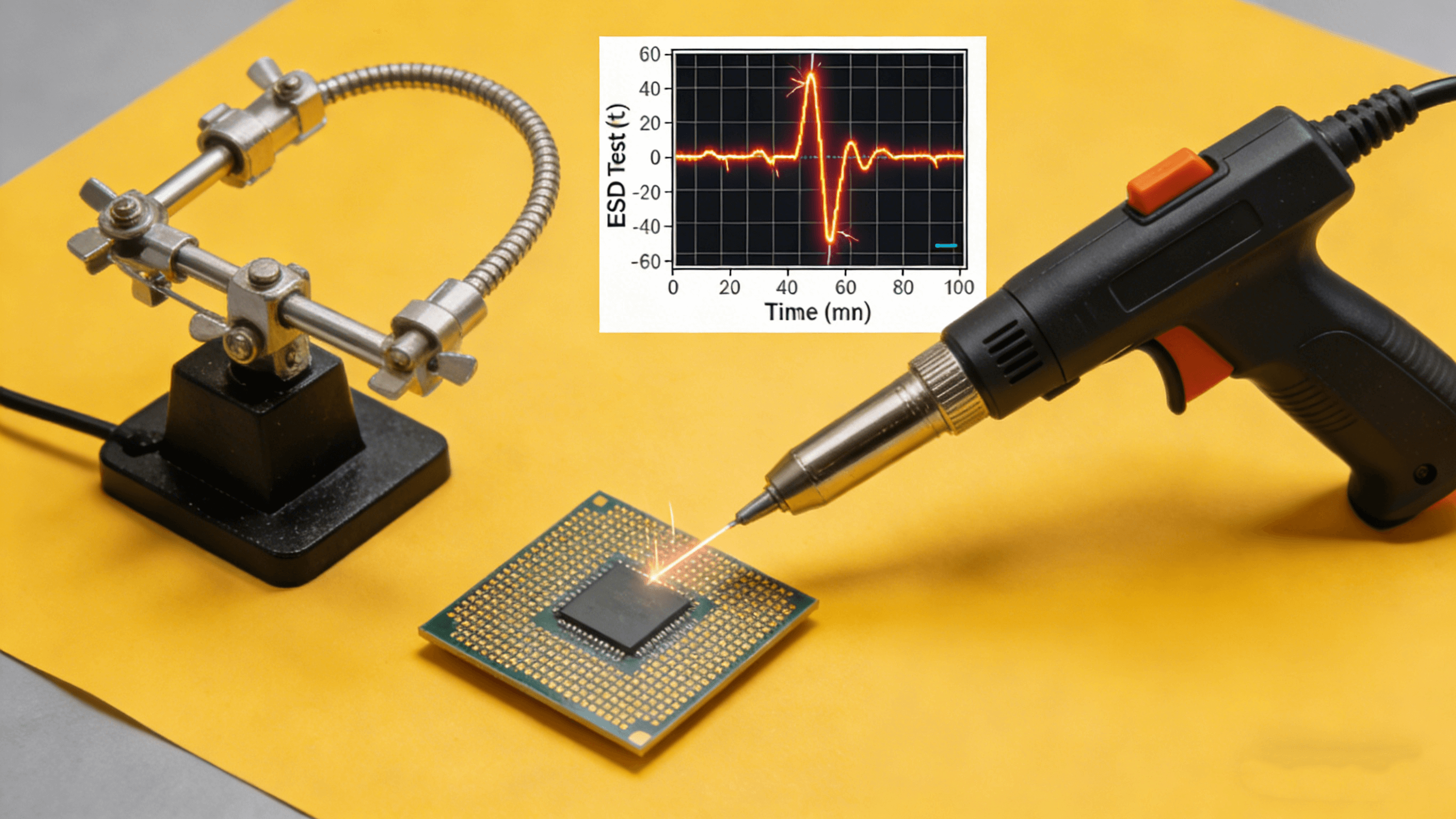

EOS测试原理

芯片级EOS测试主要采用传输线脉冲(TLP)技术,模拟长脉冲过应力。

核心原理:

- 使用方波脉冲(宽度100ns~数μs)逐步增加幅度。

- 实时测量器件电压/电流响应,绘制I-V曲线。

- 识别触发电压(Vt1)、保持电压(Vh)和二次击穿电流(It2)。

Very Fast TLP(VF-TLP)用于更短脉冲(<10ns),桥接ESD与EOS。

EOS vs ESD对比

| 项目 | ESD(静电放电) | EOS(电气过应力) |

|---|---|---|

| 持续时间 | ns级(<200ns) | 100ns ~ ms级 |

| 能量水平 | 低(mJ级) | 高(J级) |

| 波形特征 | 尖峰瞬态 | 矩形或长脉冲 |

| 损伤特征 | 局部击穿、薄层熔融 | 大面积熔融、金属重构 |

| 测试方法 | HBM/MM/CDM | TLP、长脉冲曲线追踪 |

| 防护重点 | 瞬态钳位二极管/SCR | 稳压、限流、系统级保护 |

EOS损伤更具破坏性,常导致灾难性失效。

测试流程

典型芯片级EOS测试步骤:

- 引脚组合定义:I/O to VDD/VSS、VDD to VSS等。

- 脉冲施加:从低幅度开始步进,记录漏电流。

- 曲线分析:提取关键参数,判定耐受阈值。

- 失效后验证:电参数漂移>10%或功能丢失。

- 结合失效分析:FIB/TEM观察损伤位置。

参考标准:JESD78(Latch-up)、ANSI/ESDA/JEDEC JS-001(ESD)扩展至EOS。

常见失效模式

EOS常导致以下损伤:

- 栅氧击穿:高电压下氧化层永久破坏。

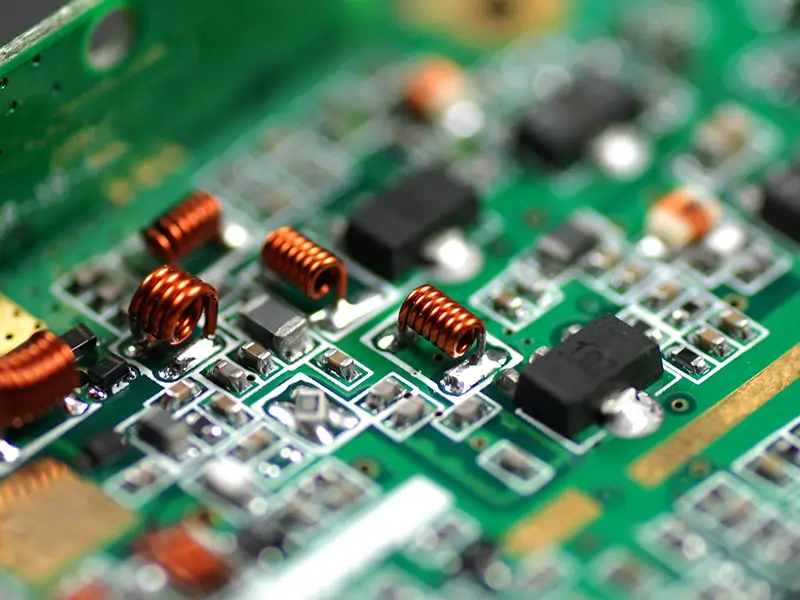

- 金属熔融/重构:过电流引起互联层熔断或铝迁移。

- PN结烧毁:热积累导致结区熔化。

- 寄生晶闸管触发:Latch-up后二次击穿。

芯片级EOS测试原理及失效模式分析是提升集成电路抗过应力能力的关键,通过TLP等精准表征,帮助企业识别防护薄弱点、优化设计,避免生产和应用中的高能量损伤风险,在高可靠性领域发挥重要作用。

深圳汇策作为专业第三方检测机构,提供芯片级EOS测试服务,配备先进TLP/VF-TLP系统及曲线追踪仪,支持晶圆级/封装级全引脚EOS耐受评估、失效模式分析及防护优化验证。我们助力客户提升芯片鲁棒性,确保产品满足AEC-Q100、工业级等严苛要求。