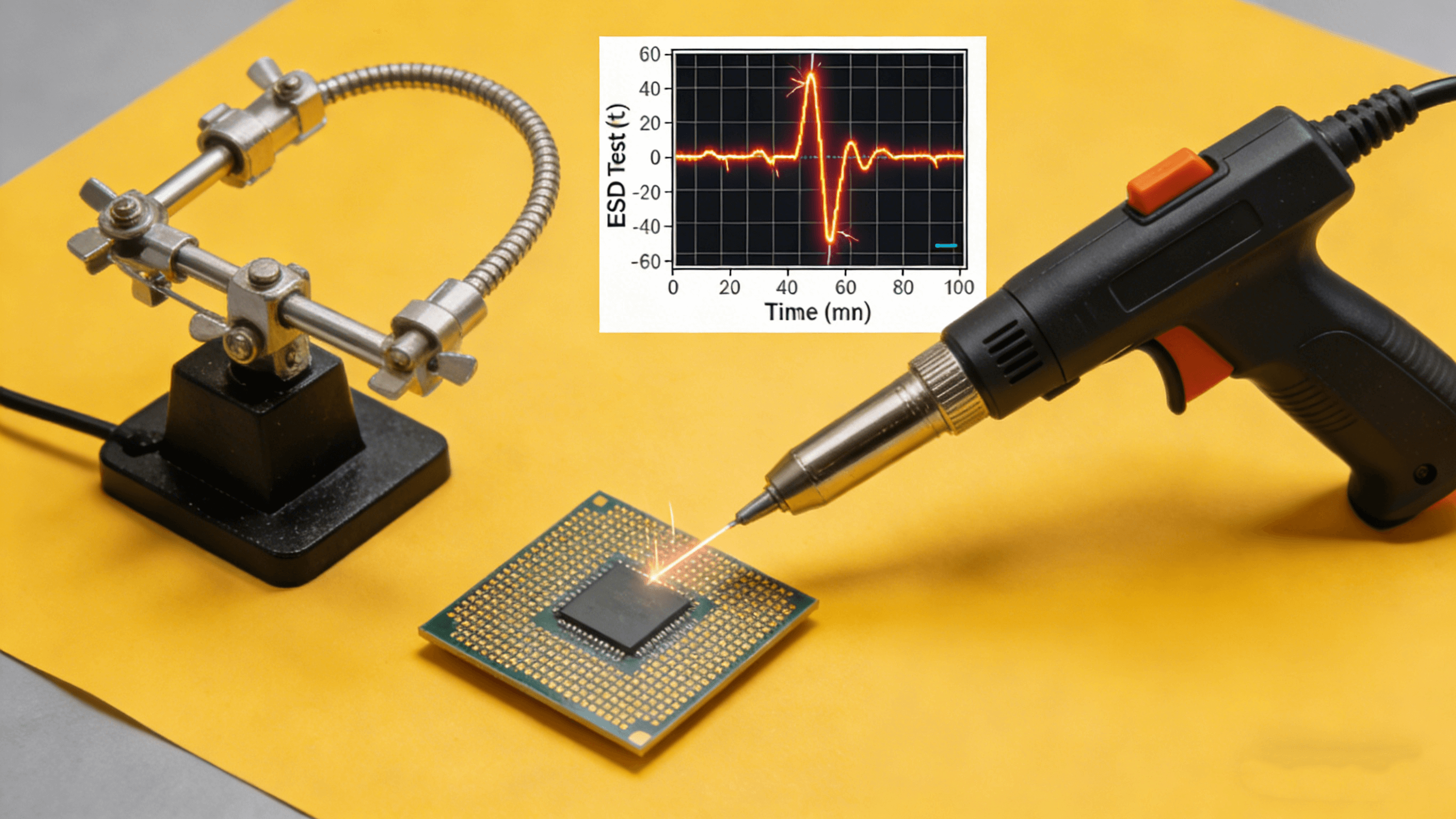

在先进制程节点下,集成电路对静电放电(ESD)的敏感度急剧上升,一次意外放电即可导致栅氧击穿或金属熔融,造成不可逆损伤。据行业统计,ESD相关失效占半导体器件场内失效的30%以上。芯片级ESD测试通过模拟不同放电模型,评估IC内部保护结构的耐受能力,帮助设计师优化防护电路,确保产品在制造、组装和使用过程中的可靠性。随着2025年第三代半导体和AI芯片的爆发,这一测试已成为芯片出厂前必不可少的质量把关环节。

ESD测试主要模型

芯片级ESD测试常用三种模型,模拟不同场景:

- HBM(Human Body Model):人体放电模型,100pF电容通过1.5kΩ电阻放电,模拟人体触碰。

- MM(Machine Model):机器放电模型,200pF电容无电阻,直接高电流放电,模拟金属工具。

- CDM(Charged Device Model):器件带电模型,器件自身带电后对地放电,峰值电流最高,适用于先进制程。

三大模型对比

| 模型 | 电容/电阻 | 峰值电流 | 放电时间 | 典型耐压要求 | 适用场景 |

|---|---|---|---|---|---|

| HBM | 100pF / 1.5kΩ | 中等 | 100ns | 2kV~8kV | 人体操作 |

| MM | 200pF / 0Ω | 高 | 10ns | 200V~400V | 自动化产线 |

| CDM | 器件自身 | 极高 | <1ns | 250V~1kV | 器件带电摩擦 |

CDM在3nm以下节点最严苛,常成为瓶颈。

测试流程

芯片级ESD测试标准流程(参考JESD22-A114/A115/C101):

- 引脚分类:区分VDD、VSS、I/O、NC引脚。

- 测试组合:PS(Pin to VSS)、PD(Pin to VDD)、NS/ND等。

- 逐步升压:从低电压开始,步进100V或50V,直至失效。

- 失效判定:漏电流超标(>1μA)或功能异常。

- 曲线记录:绘制I-V曲线评估保护结构。

常见失效模式

ESD常导致:

- 栅氧击穿(熔融孔洞)

- 金属互联熔断

- PN结烧毁

- Latch-up触发

防护优化建议

- 增加双二极管或SCR防护路径

- 优化布局降低寄生电阻

- 使用TLP(Transmission Line Pulsing)辅助表征瞬态响应

- 先进节点引入本地钳位结构

芯片级ESD测试是保障集成电路抗静电能力的核心方法,通过科学模拟和精准评估,帮助企业及早发现防护薄弱环节,提升产品 robustness,在竞争激烈的半导体市场中占据优势。

深圳汇策作为专业第三方检测机构,提供芯片级ESD测试服务,配备符合JEDEC标准的HBM/MM/CDM测试系统,支持晶圆级和封装级全引脚组合测试、TLP表征及失效分析。我们助力客户优化ESD防护设计,确保芯片满足AEC-Q100、IEC 61000-4-2等国际规范。