在电子硬件开发中,最痛苦的莫过于“改板”。一块复杂的高速PCB,从设计到打样、贴片,周期长达数周,费用高达数万。如果调试时发现DDR5跑不到额定频率,或者SerDes链路丢包严重,不得不重新改板(Re-spin),这不仅浪费金钱,更可能导致产品错失上市窗口。而信号完整性(SI)测试,就是避免这种昂贵试错的“避雷针”。

传统流程 vs SI介入流程

- 传统“盲跑”: 画图 -> 打板 -> 调试 -> 不行 -> 改图 -> 打板…

代价: 只要有一个阻抗匹配没做好,整个周期就要重来。

- SI介入流程: 前仿真 -> 画图 -> SI仿真验证 -> 打板 -> SI实测 -> 调试。

优势: 在虚拟阶段解决90%的问题,实测阶段解决剩余10%的工艺偏差。

SI测试如何精准“省钱”?

1. 阻抗板测试 (Coupon Test)

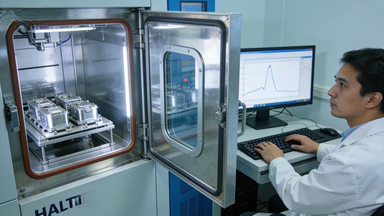

在PCB批量生产前,先切片测试阻抗条(Coupon)。如果工厂的层压工艺导致阻抗偏离了50欧姆(例如做成了45欧姆),会导致严重的反射。通过TDR测试及时发现,可以让工厂调整压合参数,避免整批板报废。

2. S参数提取与仿真校准

利用VNA提取实际PCB走线的S参数,不仅能验证当前的损耗是否达标,还能将实测数据代入仿真软件,校准仿真模型。这能让工程师对下一次改板的成功率拥有“上帝视角”。

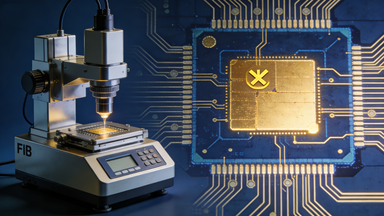

3. 快速定位“隐形”故障

有时问题出在连接器或过孔(Via)上。通过TDR(时域反射)功能,可以精确到毫米级定位阻抗突变点。

案例: 发现过孔残桩(Stub)太长导致信号反射,下一版设计只需做一个简单的背钻(Back-drill)工艺即可解决,无需更改走线。

总结

信号完整性测试不是成本的增加,而是成本的节省。它用科学的数据替代了工程师的“经验猜测”,将由于设计失误导致的改板次数降到最低。在高速时代,SI测试能力就是企业的核心研发竞争力。

上海德垲致力于为客户提供“仿真+实测”的信号完整性解决方案。我们不仅提供高端的SI测试服务,还能结合HFSS/ADS仿真工具,为您提供从原理图阶段的拓扑分析到量产阶段的阻抗管控建议,帮您一次把设计做对。