在低速电路时代,导线仅仅是导线,连接两个元件即可。然而,当信号频率攀升至GHz级别,每一条PCB走线都变成了传输线。此时,工程师们面临的最大敌人往往不是逻辑错误,而是物理层面的“回声”——信号反射。阻抗不匹配导致的反射现象,是信号完整性(Signal Integrity, SI)测试中最常见、也最棘手的问题之一,它轻则导致数据误码,重则甚至可能烧毁芯片。

什么是阻抗不匹配?水管的启示

要理解电信号的反射,我们可以想象水流在水管中流动。如果水管的直径始终保持一致,水流就会平稳地流向出口。但是,如果水管突然变细或变粗(阻抗突变),水流在交界处就会产生湍流和回波。

在高速电路中,传输线必须保持特征阻抗(通常为50Ω或100Ω差分)的连续性。当信号遇到以下情况时,就会发生阻抗不匹配:

- 过孔(Via): 信号换层时,过孔的寄生电容导致阻抗下降。

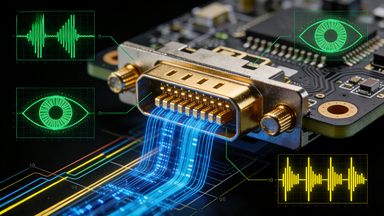

- 连接器: 接口处的结构变化往往是阻抗不连续的重灾区。

- 线宽变化: 设计疏忽或加工误差导致的走线宽度突变。

- 末端未端接: 接收端阻抗与传输线阻抗不相等。

反射带来的“三宗罪”

当信号能量无法被接收端完全吸收,剩余的能量就会像回声一样反射回源端。这种来回反弹的能量叠加在原信号上,会产生严重的波形畸变。

1. 过冲与下冲 (Overshoot & Undershoot)

反射能量叠加导致电压瞬间超过逻辑电平的上限(过冲)或低于下限(下冲)。

后果: 过冲可能击穿芯片的输入保护二极管,造成永久性损坏;下冲可能导致时序误触发。

2. 振铃 (Ringing)

由于阻抗多次不匹配,信号在源端和接收端之间反复反射,导致波形在高低电平处出现高频振荡。

后果: 这种振荡会增加系统的电磁干扰(EMI),并压缩眼图的张开度,导致误码率上升。

3. 台阶 (Stair-stepping)

信号电平无法一次上升到位,而是呈现出阶梯状上升。

后果: 导致信号上升沿变缓,严重影响高速时序的建立时间(Setup Time)。

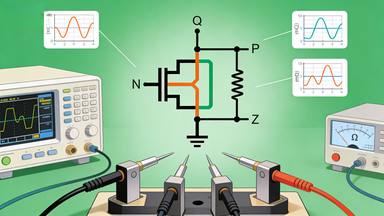

TDR测试:像雷达一样定位问题

在信号完整性测试中,我们通常使用时域反射计(TDR)来“透视”传输线的阻抗变化。TDR的工作原理类似于雷达:向线路发送一个快速阶跃脉冲,并监听反射回来的波形。

通过分析TDR波形,我们可以精准地判断阻抗不匹配的性质:

| TDR波形特征 | 物理意义 | 可能原因 |

|---|---|---|

| 波形向上凸起 | 感性不连续(阻抗偏高) | 线宽变细、跨越分割平面、连接器引脚悬空。 |

| 波形向下凹陷 | 容性不连续(阻抗偏低) | 线宽变粗、过孔寄生电容过大、焊盘面积过大。 |

| 波形平坦 | 阻抗匹配良好 | 设计符合目标阻抗(如50Ω)。 |

如何解决阻抗不匹配?

一旦在测试中发现反射问题,通常采取以下策略进行整改:

- 端接匹配: 在源端串联电阻(源端匹配)或在接收端并联电阻(终端匹配),消除反射点。

- 优化过孔: 使用盲埋孔或反钻(Back-drill)技术,减少过孔残桩(Stub)带来的反射。

- 全程阻抗控制: 严格管控PCB生产工艺,确保走线宽度和介质厚度的公差在允许范围内。

总结

反射与阻抗不匹配是高速数字系统设计的核心挑战。一个完美的电路设计,必须建立在对传输线理论的深刻理解之上。通过TDR等专业测试手段,工程师可以精准地“看见”信号在PCB上的每一次跳变,从而消除反射隐患,确保信号“原汁原味”地到达终点。

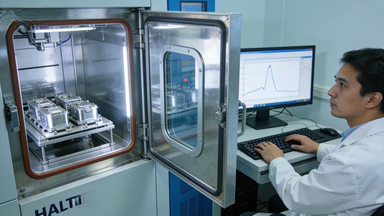

汇策-上海德垲拥有行业领先的信号完整性测试实验室,配备高达50GHz带宽的采样示波器及高精度TDR模块。我们提供从PCB阻抗板测试、S参数提取到高速互连系统的眼图分析与整改建议,助您解决最棘手的信号反射难题。